# **IBIS Model Validation Report**

Asian IBIS Summit, Shanghai China October 27, 2006

Zheng Qi

Qzheng@fiberhome.com.cn

#### overview

- IBIS Models have played an important role in signal integrity analysis

- Access Buffer Characteristics

- Buffer's transition time

- driver output impedance

- Critical Net Quality Check

- Incident Voltage

- Monotonic

- Timing Analysis

- Flight Time Calculating

- Power Integrity Analysis

#### overview

- Before playing with IBIS we have to know

- behavioral model concept

#### overview

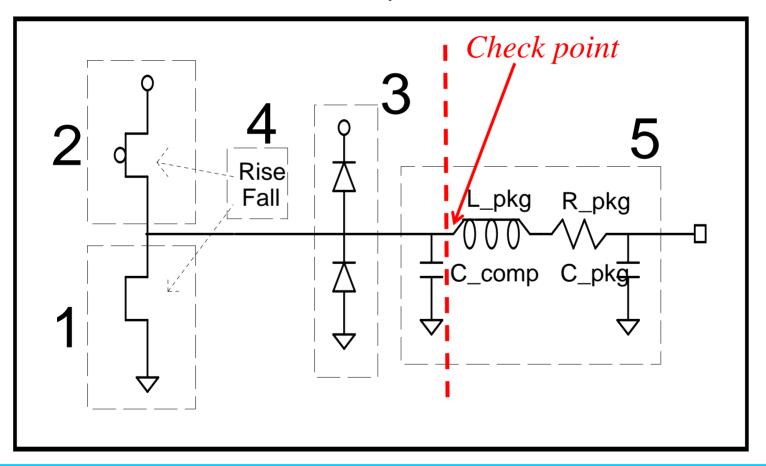

- Model Validation (Comparison)

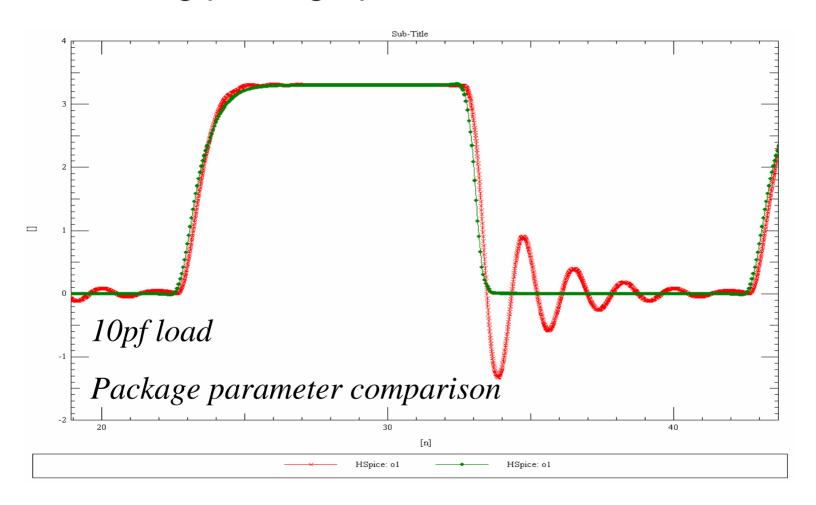

- With & without Package parameter

- Spice model Vs IBIS model

- R-fixture comparison

- Test fixture

- 50 Ω Resistor Load to GND

- 10pf Capacitor load to GND

- Model (original model from A company )

- Push-pull clock buffer

- 1R+1F

- R\_fixture = 0.50k  $\Omega$

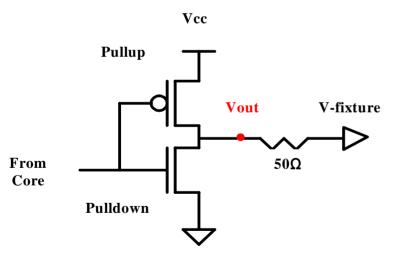

### Spice model simulation

## Removing package parameter first

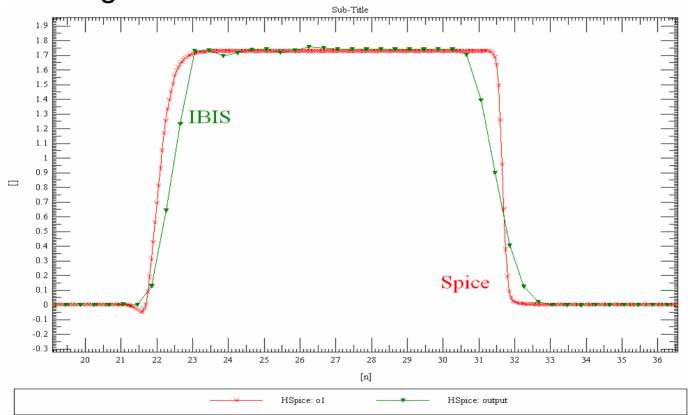

## Spice model Vs IBIS model

- Original IBIS model

- 1R+1F & R\_fixture = 0.50K  $\Omega$

- Using  $50 \Omega$  load for test

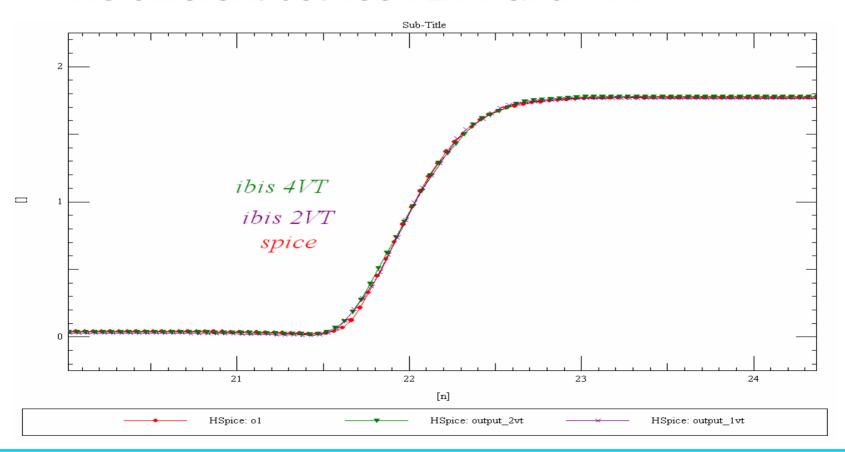

## Model adjusting

- Add two V-T curves (2R + 2F)

- $\blacksquare$  R-fixture changed to 50  $\Omega$

- Add More points on V-T curves (lower timestep)

- Rising edge matched very well ⊕

- No different between 2VT and 4VT

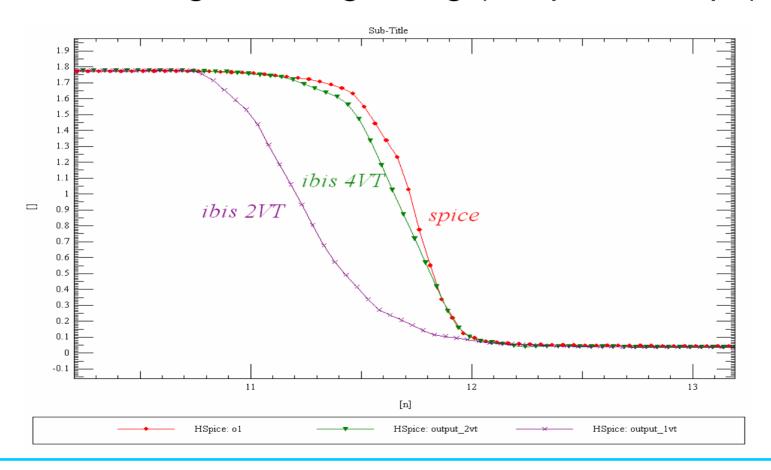

#### Model test

- 4VT Falling edge match good

- 2VT Falling time degrading (460ps → 750ps)

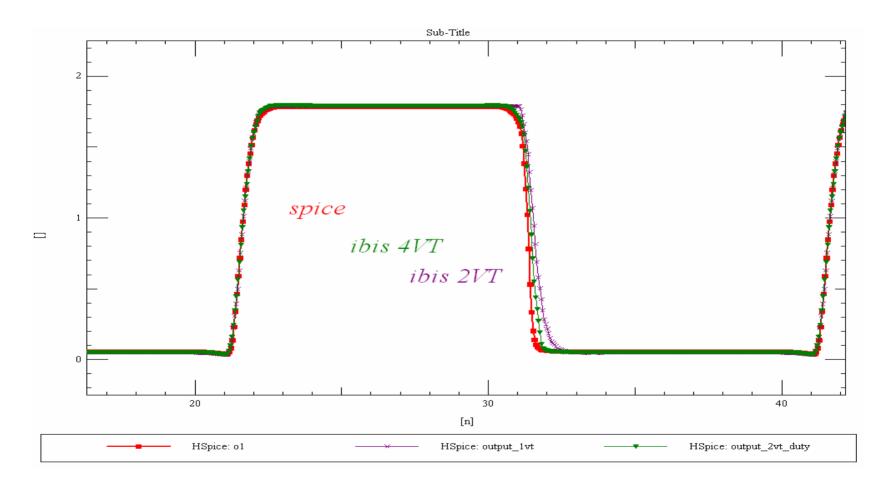

#### Model test

## Using 4VT and 2VT tables

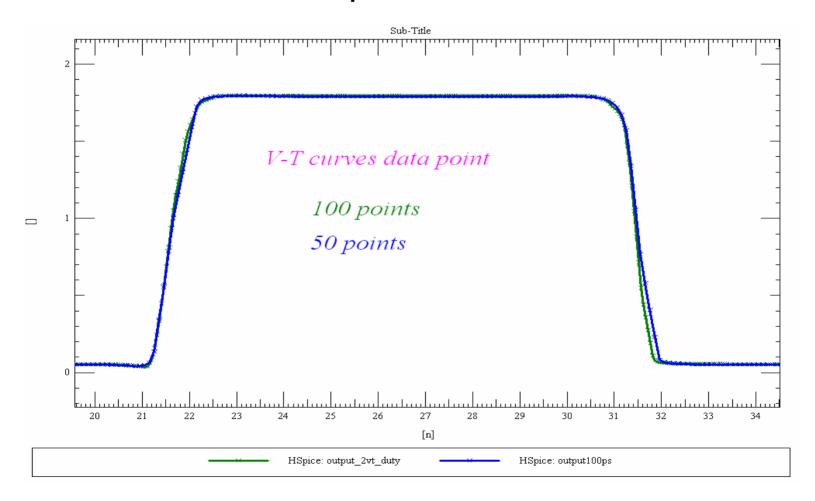

## Different V-T data points

#### Model test

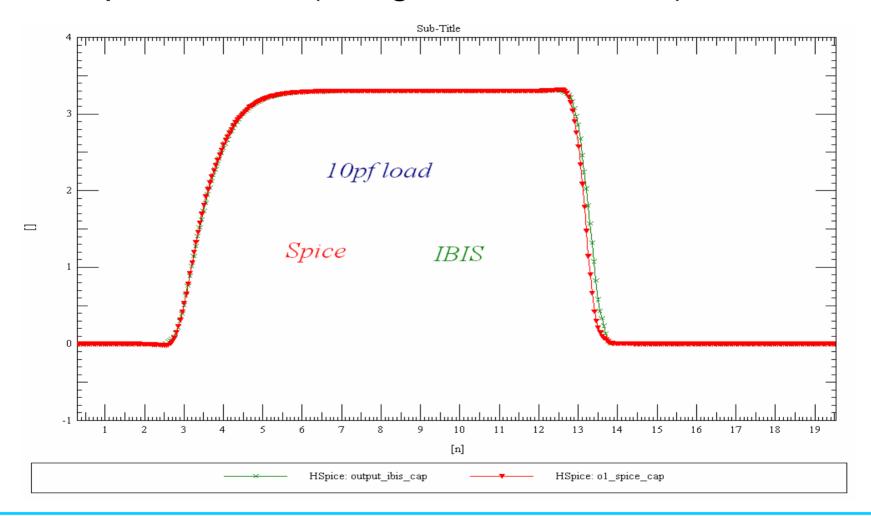

## Capacitor load (using modified model)

#### Good model

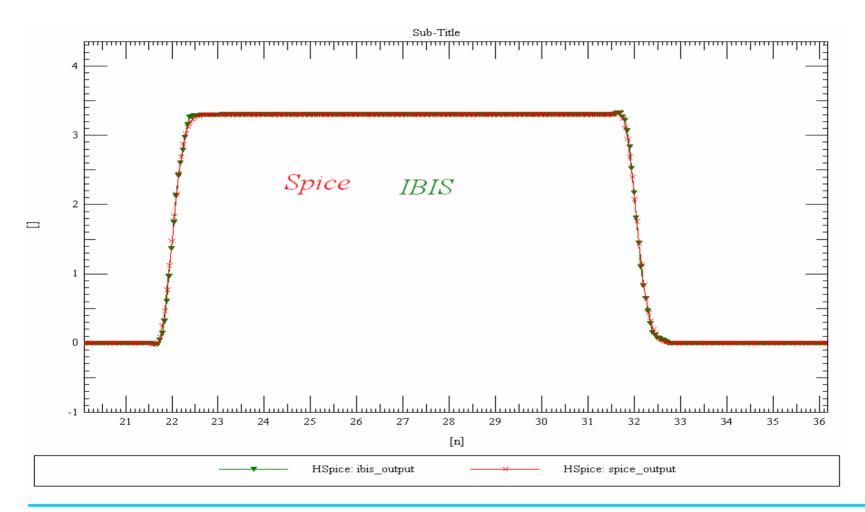

■ B model comparison (good model) 🌢

#### Conclusion

- The waveform shape (edge and DC Level) are very close between IBIS and Spice simulation when the model is correctly generated

- Downloaded models always need careful checking

- Package parameters have great impact on waveform quality

- Power pin's package parameters need more attention